台积电近日宣布,其位于美国亚利桑那州的先进封装设施计划于2028年正式动工,并导入System on Integrated Chips(SoIC)与Chip on Panel on Substrate(CoPoS)两项前沿技术,旨在进一步推动3D垂直集成与2.5D集成的发展。这一战略布局不仅标志着台积电在先进封装领域的持续深耕,也预示着半导体行业将迎来新一轮的技术革新与产能升级。

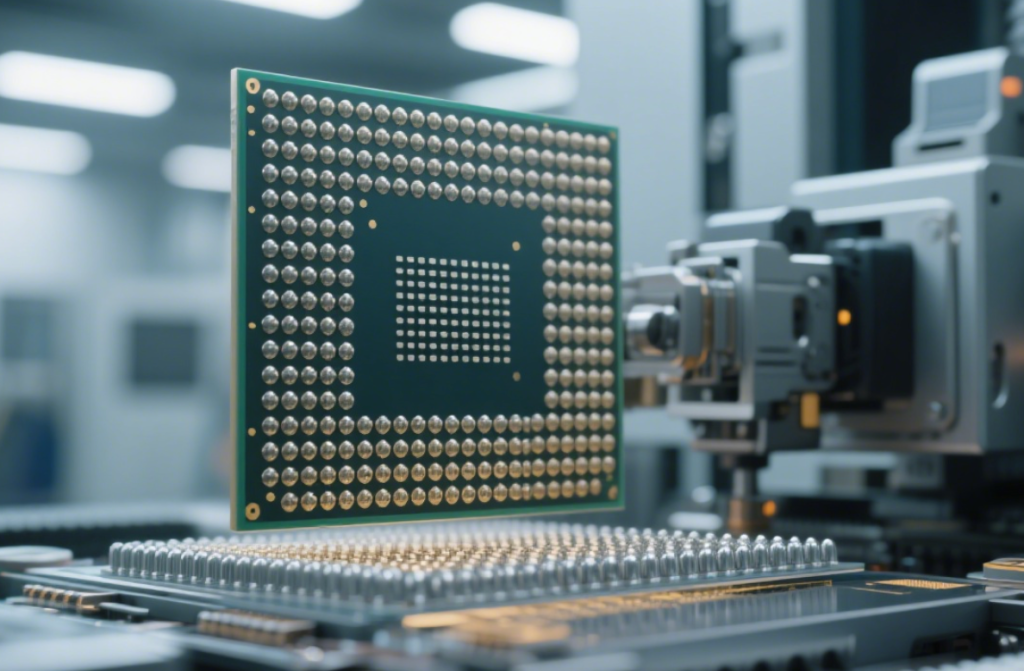

根据台积电的规划,亚利桑那州的两座先进封装厂将毗邻其拥有N2/A16节点产能的第三晶圆厂。其中,首座工厂将聚焦3D垂直集成的SoIC工艺,通过晶圆对晶圆的键合技术,实现多芯片的高密度堆叠与异质整合。SoIC技术采用无凸块的混合键合方式,最小凸点间距可达1微米,支持逻辑、内存、缓存等多类芯片的垂直集成,从而在接近相同体积下实现双倍以上的性能提升。该技术已在AMD Ryzen X3D处理器中得到验证,并计划于2026年启动测试生产,2027年完成与合作伙伴的验证工作。

第二座工厂则将应用目前尚在起步阶段的CoPoS技术,这是一种基于面板级(Panel)的2.5D集成方案。相较于传统的CoWoS(Chip on Wafer on Substrate)技术,CoPoS采用方形面板基板替代圆形晶圆,显著提升了边角利用率与单次封装面积,从而在降低成本的同时提高了产能。CoPoS技术将主要服务于人工智能(AI)、高性能计算(HPC)等对高带宽内存(HBM)与低延迟有极高需求的领域,其需方包括英伟达、AMD、博通等主要客户。台积电计划于2026年在子公司采钰设立CoPoS实验线,2028年底至2029年间实现大规模量产。

从技术维度看,3D垂直集成与2.5D集成代表了半导体封装的两大发展方向。3D集成通过芯片的垂直堆叠与TSV(硅穿孔)技术,实现了最高集成度与最短信号路径,适用于高密度存储与逻辑-内存垂直整合场景。而2.5D集成则通过中介层(Interposer)实现多芯片的横向互连,平衡了性能与成本,成为AI加速器与HPC领域的首选方案。台积电的SoIC与CoPoS技术分别在这两大领域取得了突破,其技术指标与量产进度均优于三星的X-Cube与英特尔的Foveros等同类技术。

台积电此举不仅巩固了其在先进封装领域的全球领导地位,也响应了AI芯片对高带宽内存与低延迟的迫切需求。随着SoIC与CoPoS技术的导入,台积电将能够为客户提供从逻辑工艺到先进封装的全方位解决方案,进一步推动Chiplet架构与异质整合的发展。同时,亚利桑那州工厂的落地也将缓解台积电美国客户的供应链依赖,形成与三星、英特尔三足鼎立的竞争格局,加速半导体行业向1.4纳米及以下节点的演进。