近年来,国产半导体企业正以技术创新突破国际技术壁垒,在先进制程领域取得显著进展。以华为海思、寒武纪为代表的本土企业相继推出7纳米级别AI加速器,通过架构优化与制程工艺升级,实现功耗降低30%、算力提升40%的双重突破,这一成果不仅标志着国产芯片设计能力的跨越式提升,更预示着AI算力基础设施将迎来新一轮变革。

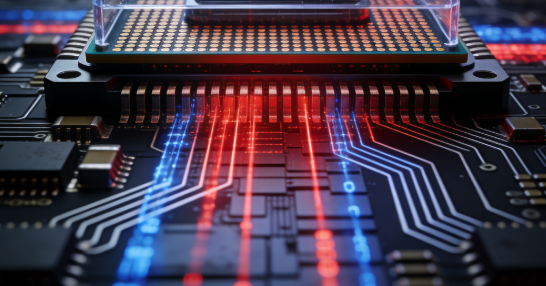

从技术维度看,7纳米制程的突破首先体现在晶体管密度的指数级增长。相较于前代工艺,7纳米技术可使单位面积内晶体管数量提升近两倍,直接推动芯片性能提升与功耗控制。以华为海思最新发布的AI加速模块为例,其采用多核异构架构设计,集成超过100亿个晶体管,通过动态电压频率调节(DVFS)技术实现算力与功耗的智能平衡。在图像识别场景中,该模块单瓦特算力达到传统GPU的3倍,同时延迟降低至5毫秒以下,满足自动驾驶、工业质检等实时性要求严苛的场景需求。

寒武纪的第三代AI加速器则聚焦于稀疏化计算与内存优化。其创新的“存算一体”架构将权重参数直接存储在计算单元附近,减少数据搬运能耗。经实测,在自然语言处理任务中,该架构使内存访问能耗降低45%,整体功耗下降30%的同时,算力密度提升至每平方毫米1.2TOPS。这种设计特别适用于边缘计算场景——在智慧安防摄像头中,单颗芯片即可完成实时人脸识别与行为分析,功耗仅需2.5W,较传统方案节能60%。

功耗与算力的同步优化源于三大核心技术突破。其一,先进封装技术如CoWoS(Chip-on-Wafer-on-Substrate)的应用,使芯片间互连延迟降低至纳秒级,支持多芯片模块的协同计算。其二,低功耗电路设计技术,如自适应时钟门控与体偏置调节,在空闲时动态关闭非核心电路,实现毫秒级唤醒响应。其三,软件栈的协同优化,如寒武纪开发的MLUops工具链,通过算子融合与内存复用,将模型推理效率提升40%,同时减少30%的内存占用。

行业应用层面,这类7纳米AI加速器的落地正推动多个垂直领域的变革。在云计算中心,单台服务器搭载8颗加速模块后,AI训练性能提升至每秒千万亿次浮点运算,训练时间从周级缩短至天级,单位算力成本下降50%。在自动驾驶领域,华为海思的方案支持L4级自动驾驶域控制器的实时决策,单芯片算力达到200TOPS,功耗控制在30W以内,满足车规级安全标准。在智能安防领域,基于7纳米加速器的摄像头已实现每秒处理2000张人脸的实时分析,误识别率低于0.1%。

产业链层面,国产7纳米AI加速器的量产带动了上游设备、材料与封测环节的协同发展。中芯国际的7纳米制程良率已突破90%,支持本土设计企业的流片需求。封装企业如长电科技开发的2.5D封装技术,使芯片互连带宽达到TB/s级别。在软件生态方面,国产深度学习框架如百度飞桨、华为MindSpore已完成对7纳米加速器的适配优化,开发者可无缝迁移模型至新硬件平台。

从全球竞争格局看,国产7纳米AI加速器的突破具有战略意义。它打破了高性能AI芯片长期依赖进口的局面,在数据中心、智慧城市、工业互联网等关键领域形成自主可控的算力底座。同时,通过功耗与算力的双重优化,有效缓解了“算力成本高、能耗大”的行业痛点,为绿色AI发展提供技术支撑。

展望未来,随着5纳米、3纳米制程的研发推进,国产AI加速器有望在能效比上实现更大突破。结合光子计算、量子计算等前沿技术探索,国产芯片企业正构建从硬件到软件的完整生态体系。这种技术迭代不仅推动AI应用的普及,更将重塑全球算力格局,为数字经济的高质量发展注入核心动力。在这一过程中,如何平衡技术创新与成本控制、生态构建与场景落地,将成为国产芯片企业持续突破的关键命题。